# Arm Scalable Vector Extension and application to Machine Learning

Dan Andrei Iliescu, Francesco Petrogalli

October 2018

White paper

#### Contents

| Int              | troduction                                        | 2  | 2        |

|------------------|---------------------------------------------------|----|----------|

| I                | The Scalable Vector Extension                     | 2  | <u>)</u> |

| 2                | SVE ACLE SVE intrinsic functions                  |    | 3        |

| 3                | ML algorithms with VLA SVE  Matrix multiplication | 9  | 7        |

| 4                | Tools                                             | 15 | ;        |

| Acknowledgements |                                                   | 16 | ,        |

| Trademarks       |                                                   | 16 | í        |

| Changelog        |                                                   | 16 | į        |

| References       |                                                   | 16 | ,        |

## Introduction

In this document we present code examples that show how to vectorize some of the core computational kernels that are part of machine learning system.

The examples presented in this document are written with the Vector Length Agnostic (VLA) approach introduced by the Scalable Vector Extension (SVE).

In particular, the paper shows how VLA techniques can be used to efficiently vectorize General Matrix Multiplication (GEMM) and low precision GEMM (GEMMlowp) computational kernels.

## I The Scalable Vector Extension

SVE is a vector extension for AArch64 execution mode for the A64 instruction set of the Armv8 architecture. Unlike other SIMD architectures, SVE does not define the size of the vector registers, but constrains into a range of possible values, from a minimum of 128 bits up to a maximum of 2048 in 128-bit wide units. Therefore, any CPU vendor can implement the extension by choosing the vector register size that better suits the workloads the CPU is targeting. Instructions are provided specifically to query an implementation for its register size, to guarantee that the applications can run on different implementations of the ISA without the need to recompile the code.

Most of the instructions of the extension also use predicate registers to mask the lanes for operating on partial vectors. The SVE instruction set also provides gather loads and scatter stores, plus truncating stores, and signed/unsigned extended loads.

The following documents describing the architecture extension are available:

• SVE architecture reference manual (ARM limited 2017a), which defines the instructions and the registers;

- A Sneak Peak to SVE and VLA programming (Petrogalli 2016), a whitepaper with assembly examples of loops vectorized with the SVE instructions;

- The ARM Scalable Vector Extension (Stephens et al. 2017).

This document focuses on the interface at C/C++ level for SVE that is provided via the SVE Arm C Language Extensions (SVE ACLE) (ARM limited 2017b).

## 2 SVE ACLE

The SVE ACLE (or ACLE hereafter) is a set of functions and types that exposes the vectorization capabilities of SVE at C/C++ level.

They introduce a set of size-less types and intrinsic functions that a C/C++ compiler can directly convert into SVE assembly. The function-to-instruction mappings are not one to one, as some of the architectural details of the instruction set can be resolved by a compiler. For example, there is no need to expose at C/C++ level some of the addressing modes of the load and store instructions of SVE.

The ACLE introduces size-less data types in the form sv [type], where sv stands for *Scalable Vector* and type can be any of the scalar types supported by the lanes of the SVE vectors. These size-less types cover SVE vectors consisting of 8, 16, 32 and 64 bit lanes for signed and unsigned integral types, and 16, 32 and 64 bit lanes for floating point types:

- sv[u]int[8|16|32|64]\_t;

- svfloat[16|32|64]\_t.

An additional svbool\_t type is defined to represent predicates for masking operations. The predicate type carries one bit for each byte in the data types.

#### **SVE** intrinsic functions

The naming convention of the intrinsic functions in the SVE ACLE is described in detail in section 4 of the SVE ACLE document (ARM limited 2017b).

Most of them are in the form: svbase [\_disambiguator] [\_type0] [\_type1]...[\_predication].

For example, the name of the intrinsic svadd\_n\_u16\_m, with signature svuint16\_t svadd\_n\_u16\_m(svbool\_t pg, svuint16\_t op1, uint16\_t op1), describes a vector addition (add) of unsigned 16-bit integer (u16), where one of the arguments is a scalar (n) and the predication mode is merging (n).

Some of the functions, like loads and stores, have a different form for the names, with additional tokens that specify the addressing mode. For example, the function svld1\_gather\_u32base\_offset\_s32, with signature svint32\_t svld1\_gather\_u32base\_offset\_s32(svbool\_t pg, svuint32\_t bases, int64\_t offset)

is a gather load (ld1\_gather) of signed 32-bit integer (\_s32) from a vector of unsigned 32-bit integer base addresses (\_u32base) plus an offset in bytes (\_offset).

The SVE ACLE are compatible with C++ overloading and C \_Generic association, so that the names can be contracted removing those parts that can be derived from the arguments types. For example, the svadd\_n\_u16\_m can be contracted to svadd\_m, and svld1\_gather\_u32base\_offset\_s32 can be contracted to svld1\_gather\_offset.

All the examples of this document use the short form. For simplicity, we also assume no aliasing, meaning that all the pointers passed as function parameters are to be considered as restrict pointers.

#### Example

A basic example that shows how to transform a scalar loop into VLA form using the SVE ACLE is shown in listing 2.1.

#### Listing 2.1 VLA vectorization example using the SVE ACLE.

```

// Scalar version.

void add_arrays(double *dst, double *src, double c, const int N) {

for (int i = 0; i < N; i++)</pre>

3

dst[i] = src[i] + c;

}

5

6

// Vector version

7

void vla add_arrays(double *dst, double *src, double c, const int N) {

for (int i = 0; i < N; i += svcntd()) {</pre>

9

svbool_t Pg = svwhilelt_b64(i, N);

10

svfloat64_t vsrc = svld1(Pg, &src[i]);

П

svfloat64_t vdst = svadd_x(Pg, vsrc, c);

12

svst1(Pg, &dst[i], vdst);

13

14

}

15

```

The vector version in vla\_add\_arrays of listing 2.1 works as follows.

First, the header of the vector loop is issued (line 9). The number of lanes that one iteration of the vector loop can process is unknown at compile time. This means that the induction variable i needs to be incremented dynamically with the svcntd() function, which returns the number of 64-bit (double-word) lanes in an SVE vector type, or VL.D hereafter.

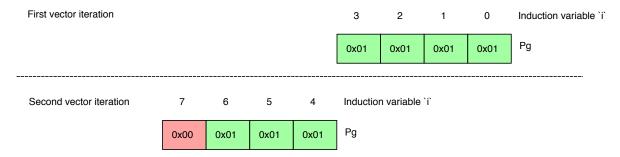

In the body of the loop, the predicate Pg is set with the whilelt\_b64 function (line II). This function builds a predicate by testing the i < N inequality for all the values of the induction variable spanning the iteration of the vector loop and associating its result to the correspondent lane of the vector register. At iteration i, it computes j < N for j=i, i+1, ..., i+VL.D-1. The 64-bit lanes view of the predicate is specified by the \_b64 part of the intrinsic, which cannot be contracted into the intrinsic name because of C scalar promotion.

On a 256-bits implementation, the value of the predicate Pg would look as follows in the second iteration of the loop in the example where  $\mathbb{N}=7$ :

```

MSB LSB

Pg = [00000000 00000001 00000001]

7 6 5 4 64-bit lanes index 'i'

```

Using the predicate Pg effectively removes the need to deal with the remainder of the loop that would not fit in a full vector. The predicate values over the full loop iteration for the 256-bit example where  $\mathbb{N}=7$  are shown in figure 1.

# 3 ML algorithms with VLA SVE

#### Matrix multiplication

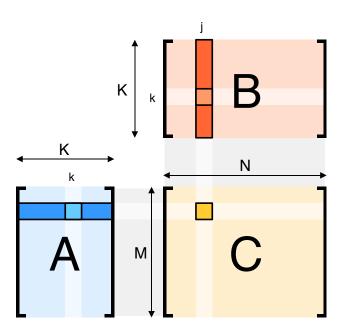

Matrix multiplication is one of the most widely used operations in machine learning. It is a binary operation that takes as input two matrices (A of dimensions (M, K) and B of dimensions (K, N)) and returns as output one

Figure 1: Predication.

matrix (C of dimensions (M,N)) in which every element  $C_{ij}$  is the dot product of row i of matrix A with column j of matrix B.

The dot product of two arrays, X and Y, of equal length, N, is computed by multiplying each element of one array with its corresponding element in the other array, and then summing up all the products.

$$Z = \sum_{n=1}^{N} X_n * Y_n$$

The dot product of two arrays can be implemented in C as in listing 3.1.

#### Listing 3.1 C implementation of the dot product of two arrays of the same size.

```

double dot(double *X, double *Y, int N) {

double Z = 0;

for (int n = 0; n < N; ++n)

Z += X[n] * Y[n];

}</pre>

```

To multiply two matrices, we perform the dot product for every row of matrix  ${\cal A}$  with every column of matrix  ${\cal B}$ .

$$\forall i \in [1:M], \; \forall j \in [1:N], \; C_{i,j} = \sum_{k=1}^K A_{i,k} * B_{k,j}$$

In this document we assume that matrices of size (S,T) are implemented as C arrays of length S\*T where element (s,t) is at memory offset (s\*T+t), hence in row-major order. Using this convention, matrix multiplication can be implemented as in listing 3.2.

#### **Listing 3.2** C implementation of matrix multiplication.

```

void mm(double *C, double *A, double *B, long M, long N, long K) {

for (long i = 0; i < M; ++i)

for (long j = 0; j < N; ++j) {

C[i * N + j] = 0;

for (long k = 0; k < K; ++k)

C[i * N + j] += A[i * K + k] * B[k * N + j];

}

</pre>

```

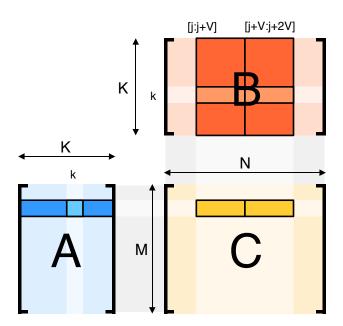

Figure 2: Matrix Multiplication. The blue row of A is multiplied with the red column of B to produce the yellow element of C.

#### Simple vectorization

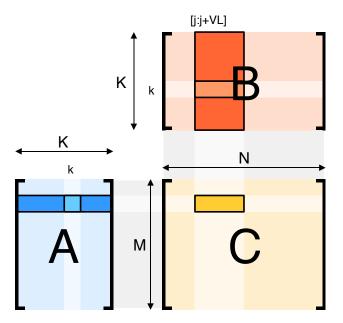

Matrix multiplication has great potential for parallelization due to the repetitive nature of the operations involved and the layout of the data. For instance, each element of row i of the resulting matrix C is the dot product of row i of matrix A with the corresponding column of matrix B. Therefore, we can compute a batch of VL elements of row i of matrix C at once by computing the dot products of row i of matrix A with a batch of VL columns of matrix B in figure 3.

For describing the algorithm of the examples in this and the following sections, we introduce the notation  $A_{a,[b:c]}$  to represent the sub-matrix of a matrix A containing the elements of row a between columns b and c.

Let's considers a batch of VL columns of matrix B as a single-column matrix of size (K,1) whose elements are arrays of size VL. If we multiply each of these arrays of matrix B with the corresponding scalar element of matrix A, and then sum up the results, we get an array of size VL which is equivalent to the batch of VL elements of row i of the resulting matrix C.

$$C_{i,[j:j+VL]} = \sum_{k=1}^{K} A_{i,k} * B_{k,[j:j+VL]}$$

We achieve this algorithmically by carrying a rectangular stencil, [j:j+VL], of size (K,VL) (where VL is the number of elements in an SVE register) in steps of VL over matrix B. The stencil starts at column j and sits over at most VL columns of matrix B. The columns of matrix B that are contained within the stencil represent the batch of VL columns that will be multiplied with row i of matrix A to result in its corresponding batch of elements of row i of matrix C in figure 3.

So, for every row i in matrix A, and for every stencil [j:j+VL] in matrix B, we record in a predicate how many columns of matrix B are actually contained within the stencil (in case N is not a multiple of VL and the current stencil goes over the border of the matrix), then we compute the dot product between row i and columns [j:j+VL] by multiplying the corresponding elements and adding them up, and we store the result in  $C_{i,[j:j+VL]}$ .

The code shown in listing 3.3 presents a vectorized version of a half-precision (16-bit floating point) matrix multiplication.

Figure 3: Vectorized Matrix Multiplication. The blue row of A is multiplied with the columns in the red stencil of B to produce the yellow vector of C.

#### Listing 3.3 Half-precision matrix multiplication with VLA vectorization.

```

void hgemm 01(float16 t *C, float16 t const *A, float16 t const *B,

ı

const unsigned long M, const unsigned long K,

2

3

const unsigned long N) {

for (unsigned long i = 0; i < M; ++i)</pre>

for (unsigned long j = 0; j < N; j += svcnth()) {</pre>

5

svfloat16_t Acc = svdup_f16(0);

6

const svbool_t pred_j = svwhilelt_b16(j, N);

for (unsigned long k = 0; k < K; ++k) {</pre>

8

const svfloat16_t A_i_k = svdup_f16(A[i * K + k]);

9

const svfloat16_t B_k_j = svld1(pred_j, &B[k * N + j]);

10

Acc = svmla_x(pred_j, Acc, A_i_k, B_k_j);

П

12

svst1(pred_j, \&C[i * N + j], Acc);

13

}

14

}

15

```

Line 5: svcnth() is an SVE ACLE function that returns the value VL.H, representing the number of lanes of an SVE vector with 16-bit (H, from half-word) subdivision.

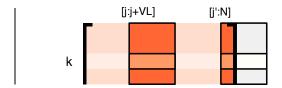

Line 7: Mark the elements of the predicate  $pred_j$  with a 2-bit subdivision as active if the corresponding element in the current stencil sits inside the matrix B, and as inactive if the element is outside the borders of the matrix. We will end up with min(VL.H, N-j) active elements. This is implemented with the SVE ACLE function  $p = svwhilelt_b16(a, b)$  which activates the n-th element of p if and only if a+n < b (see figure 4).

Line II: Add to the accumulator Acc, that was set to zero on line 6, the dot product of an array of VL.H copies of element A[i][k] with the array B[k][j:j+VL.H]. The SVE ACLE function  $a = svmla_x(pred, b, c, d)$  assigns to a the value b+c\*d. This accumulation operation is guarded by the predicate  $pred_j$ , which guarantees that the inactive elements are not processed.

Figure 4: Stencil Overflow. The lanes of the stencil on the right that overflow the border of the matrix are not used for computation. Therefore, they are set inactive.

Page 8 of 16 1.0

#### Unrolled vectorization

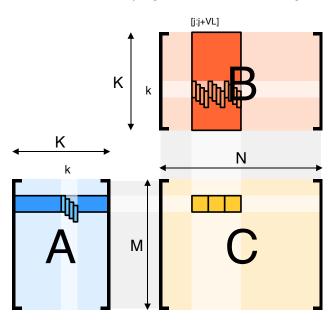

A further improvement (from the perspective of using more registers) to the computation of the matrix product implemented in listing 3.3 is to use two consecutive stencils, [j:j+VL.H-1] and [j+VL.H:j+2\*VL.H-1], and, thus, compute 2\*VL.H elements of the matrix C at once (see listing 3.4, and figure 5 for a graphical representation of the unrolling of the stencils).

**Listing 3.4** Half-precision unrolled matrix multiplication with VLA vectorization.

```

void hgemm_unrolled(float16_t *C, float16_t const *A, float16_t const *B,

const unsigned long M, const unsigned long K,

const unsigned long N) {

3

const svbool_t all_active = svptrue_b16();

5

for (unsigned long i = 0; i < M; ++i)</pre>

6

for (unsigned long j = 0; j < N; j += 2 * svcnth()) {

svfloat16_t Acc_0 = svdup_f16(0);

8

svfloat16_t Acc_1 = svdup_f16(0);

const svbool_t pred_j_1 = svwhilelt_b16(j + svcnth(), N);

10

const svbool_t pred_j_0 = svptest_first(all_active, pred_j_1)

11

? all_active

12

: svwhilelt_b16(j, N);

13

for (unsigned long k = 0; k < K; ++k) {

14

const svfloat16_t A_i_k = svdup_f16(A[i * K + k]);

15

const svfloat16_t B_k_j = svld1_vnum(pred_j = 0, \&B[k * N + j], 0);

16

const svfloat16_t B_k_j = svld1_vnum(pred_j_1, &B[k * N + j], 1);

17

Acc_0 = svmla_x(pred_j_0, Acc_0, A_i_k, B_k_j_0);

18

Acc_1 = svmla_x(pred_j_1, Acc_1, A_i_k, B_k_j_1);

19

}

20

svst1_vnum(pred_j_0, &C[i * N + j], 0, Acc_0);

21

svst1_vnum(pred_j_1, &C[i * N + j], 1, Acc_1);

22

}

23

}

24

```

Line 4: The SVE ACLE function svptrue\_b16() returns a vector predicate of all active lanes, with a 16-bit data subdivision.

Line II: We can save unnecessary computation by not calling the  $svwhilelt_b16()$  function for the first stencil when we know that it fits completely into the matrix boundaries. We can assume this happens if the second stencil sits over at least one column of B. This can be verified by testing if the first lane of the predicate corresponding to the second stencil (pred\_j\_1 in line I0) is active, by using the SVE ACLE function  $svptest_first(a, b)$ . This tests if the first element of predicate b is active.

Line 16 and 17: The svld1\_vnum intrinsic exposes the register plus immediate addressing mode of SVE. The third argument imm of the intrinsics represent a VLA offset from the base address addr. In the specific case of this example, where 16-bit data is used, the address of the load is computed with base + VL.H \* imm. This addressing mode enables loading of consecutive intervals of data that fit into multiple vectors on any SVE implementation, without the need to recompile the code to target a new vector width.

Page 9 of 16 1.0

Figure 5: Unrolled Vectorized Matrix Multiplication.

#### Dot products

An array of matrices X of dimensions (A,B,C) is an array of A matrices with B rows and C columns. Element  $X^a_{b,c}$  is the element of matrix a that sits on row b and column c.

A dot product of two arrays of matrices A of dimensions (W,M,K) and B of dimensions (W,K,N), is a matrix C of dimensions (M,N) where each element  $C_{i,j}$  is the sum of the dot products of each row i from the matrices of array A with the column j from the corresponding matrix of array B.

$$\forall i \in [1:M], \quad \forall j \in [1:N], \quad C_{i,j} = \sum_{n=1}^{W} \sum_{k=1}^{K} A_{i,k}^n * B_{k,j}^n$$

Due to commutativity, we can switch the sums around and, thus, treat the result  $C_{i,j}$  as the sum of the dot products of each element of row i from matrix A with its corresponding element of column j from matrix B, where the elements of matrices A and B are arrays of length W.

$$\sum_{n=1}^{W} \sum_{k=1}^{K} A_{i,k}^n * B_{k,j}^n = \sum_{k=1}^{K} \sum_{n=1}^{W} A_{i,k}^n * B_{k,j}^n$$

In machine learning, it is very common to process arrays of matrices of 8-bit unsigned data to obtain 32-bit results via such operations, without loss of information due to the accumulation of the product of 8-bit data into the 32-bit accumulator.

We can implement these matrices of arrays as normal matrices of 32-bit elements, but where each 8-bit lane of each element is an element in its own (see figure 6). We will refer to the 32-bit lanes as *quadruplets* of 8-bit elements. A C++ implementation of the GEMMlowp algorithm is shown in listing 3.5.

Figure 6: Low Precision

#### Listing 3.5 C++ implementation of GEMMlowp

```

void gemmlowp_c(uint32_t *C, const uint32_t *A, const uint32_t *B, size_t M,

I

size_t K, size_t N) {

2

for (size_t i = 0; i < M; ++i)</pre>

3

for (size_t j = 0; j < N; ++j)

for (size_t k = 0; k < K; ++k) {

5

uint8_t *dataA = (uint8_t *)&A[i * K + k];

uint8_t *dataB = (uint8_t *)&B[k * N + j];

uint32_t tmp = 0;

for (size_t s = 0; s < 4; ++s, ++dataA, ++dataB)</pre>

9

tmp += static_cast<uint32_t>(*dataA) * static_cast<uint32_t>(*dataB);

10

П

C[i * N + j] += tmp;

12

}

13

}

14

```

Page 12 of 16 1.0

The GEMMlowp code in listing 3.5 can be vectorized by processing more than one multiplication from the dot product at a time. This implies loading VL elements from a column in matrix B, performing the multiplications and then summing up the results listing 3.6.

#### Listing 3.6 VLA version of GEMMlowp

```

void gemmlowp_acle(uint32_t *C, const uint32_t *A, const uint32_t *B, size_t M,

size_t K, size_t N) {

2

const svint32_t index = svindex_s32(0, N);

3

for (size_t i = 0; i < M; ++i)</pre>

5

for (size_t j = 0; j < N; ++j)

6

for (size_t k = 0; k < K; k += svcntw()) {</pre>

const svbool_t pred_k = svwhilelt_b32(k, K);

8

const svuint32_t vA = svld1(pred_k, &A[i * K + k]);

9

const svuint32_t vB =

10

svld1_gather_index(pred_k, &B[k * N + j], index);

П

svuint32_t tmp = svdot(svdup_u32(0), svreinterpret_u8_u32(vA),

12

svreinterpret_u8_u32(vB));

13

C[i * N + j] += svaddv(pred_k, tmp);

14

}

15

}

16

```

The code in listing 3.6 works as follows:

Line 3: Instruction  $svindex_s32(0, N)$  builds a vector register where each element is equal to its index times N.

Line II: In order to load part of a column from B into a vector register, we need to load the first element from the address B[k\*N+j], followed by VL-1 elements in the same column, which are stored N words apart from each other. This requires loading non-consecutive addresses, which can be done using  $svld1_gather_s32index_u32()$ .

Line 12: The svdot\_u32 operation performs the dot products of each quadruplets in its two 8-bit input registers, and stores the results in the correspondent 32-bit lane of the output vector register, without loss of precision.

Line 14: svaddv\_u32() sums all the elements in the argument vector into a scalar.

Page I3 of I6 1.0

In the next implementation in listing 3.7, we optimise the process (from the perspective of increasing register pressure) by loading four quadruplets from A at a time and computing the dot products with VL quadruplets from B.

Listing 3.7 GEMMlowp with higher register pressure

```

void gemmlowp_acle_v3(uint32_t *C, const uint32_t *A, const uint32_t *B,

size_t M, size_t K, size_t N) {

2

for (size_t i = 0; i < M; ++i)</pre>

3

for (size_t j = 0; j < N; j += svcntw()) {</pre>

const svbool_t pred_j = svwhilelt_b32(j, N);

5

svuint32_t tmp = svdup_u32(0);

6

size t k = 0;

if (K > 3)

for (; k < K - 3; k += 4) {

svuint32_t vA = svld1rq(svptrue_b32(), &A[i * K + k]);

10

const svuint32_t vB0 = svld1(pred_j, &B[k * N + j]);

11

const svuint32_t vB1 = svld1(pred_j, &B[(k + 1) * N + j]);

12

const svuint32_t vB2 = svld1(pred_j, &B[(k + 2) * N + j]);

13

const svuint32_t vB3 = svld1(pred_j, &B[(k + 3) * N + j]);

14

tmp = svdot_lane(tmp, svreinterpret_u8_u32(vB0),

15

svreinterpret_u8_u32(vA), 0);

16

tmp = svdot_lane(tmp, svreinterpret_u8_u32(vB1),

17

svreinterpret_u8_u32(vA), 1);

18

tmp = svdot_lane(tmp, svreinterpret_u8_u32(vB2),

19

20

svreinterpret_u8_u32(vA), 2);

tmp = svdot_lane(tmp, svreinterpret_u8_u32(vB3),

21

svreinterpret_u8_u32(vA), 3);

22

}

23

// process tail

24

for (; k < K; k += 1) {

25

svuint32_t vA = svdup_u32(A[i * K + k]);

26

const svuint32_t vB = svld1(pred_j, &B[k * N + j]);

27

tmp = svdot(tmp, svreinterpret_u8_u32(vA), svreinterpret_u8_u32(vB));

28

}

29

30

svst1(pred_j, \&C[i * N + j], tmp);

}

31

}

32

```

The code in listing 3.7 works as follows.

Line 10: We want to load four 32-bit elements from A and repeat them in the register. The instruction svld1rq(), load replicate, fills every 128-bit subdivision of the vector register with the same four 32-bit elements from the memory address it is provided. A rendering of a vector loaded from address int \*X is shown in listing 3.8.

Line 15: We want to compute the dot product of each of the four 32-bit quadruplets of 8-bit elements from A with every 32-bit quadruplet of 8-bit elements from B, and store the results as 32-bit numbers in a vector register. The instruction svdot\_lane() will compute the dot product of each 32-bit quadruplet of the second argument with the indicated quadruplet of the third argument, without loss of precision. The quadruplet of each 128-bit chunk of A is selected with an index from 0 to 3. Because A[i], ..., A[i+3] are replicated in each

Page 14 of 16 1.0

128-bit block of vA, the four invocations of svdot\_lane() in lines 15-21 realize the same operation performed by the loop in line 15 of listing listing 3.5, for a full vector of quadruplets loaded from B.

Listing 3.8 Example of load replicate from a pointer to 32-bit data.

The version of germlowp in listing 3.7 delivers better performance than the one in listing 3.6 since:

- I. Unrolling the loop four times enabled usage of a high-performing pair of load-replicate-128b (svld1rq) and indexed-dot (svdot\_lane) instructions. A high latency gather load instruction is not needed anymore.

- 2. The inner loop of listing 3.7 is implemented with five contiguous loads and four indexed-dot instructions achieving a balanced ratio of load and multiply instructions. In listing 3.6 two loads were required for each dot instruction.

## 4 Tools

The code snippets presented in this whitepaper can be compiled to SVE object files using Arm Compiler for HPC, which fully support the SVE ACLE. The intrinsics are recognised automatically when -march=armv8+sve.

```

$> armclang -march=armv8+sve -c filename.c -o objectfile.o

```

Arm Compiler also supports automatic vectorisation that targets SVE VLA vectorisation techniques when -march=armv8+sve is invoked in conjunction with the usual flag that enables the loop vectoriser, -floop-vectorze, which is enabled by default from the optimisation level -02.

As part of our simulation tools, a user space simulator is also provided to emulate programs that include SVE instructions. The simulator, called *Arm Instruction Emulator* (*ArmIE*), execute natively on AArch64 hardware and simulate only the SVE instructions.

ArmIE can execute SVE instruction for any size of the vector registers, from the minimal 128-bit to the maximum 2048-bit width. For example, the simulation of an SVE executable program for a 256-bit implementation of SVE is invoked as follows:

```

$> armie -msve-vector-bits=256 ./program

```

Both Arm Compiler for HPC and ArmIE are available on the Arm Developer website.

Copyright © 2017 ARM Limited or its affiliates. All rights reserved.

Page 15 of 16 1.0

<sup>&</sup>lt;sup>1</sup>https://developer.arm.com/hpc

**ARM** White paper

# Acknowledgements

The authors would like to thank the following people for their help and advice: Richard Sandiford, David Mansell, Geraint North, Julie Gaskin, Jelena Milanovic, and Renato Golin.

## **Trademarks**

The trademarks featured in this document are registered and/or unregistered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. All other marks featured may be trademarks of their respective owners. For more information, visit Arm website<sup>2</sup>.

# Changelog

Version 1.0 Address reviews from Jelena Milanovic and Renato Golin.

Version 1.0-alpha Initial release.

## References

Petrogalli, Francesco. 2016. "A Sneak Peek into Sve and Vla Programming." ARM Limited. https://developer.arm.com/hpc/a-sneak-peek-into-sve-and-vla-programming.

Stephens, Nigel, Stuart Biles, Matthias Boettcher, Jacob Eapen, Mbou Eyole, Giacomo Gabrielli, Matt Horsnell, et al. 2017. "The ARM Scalable Vector Extension." *IEEE Micro* 37 (2). Institute of Electrical; Electronics Engineers (IEEE): 26–39. https://doi.org/10.1109/mm.2017.35.

ARM limited, ed. 2017a. "ARM Architecture Reference Manual Supplement - the Scalable Vector Extension (Sve), for Armv8-a." 2017. https://developer.arm.com/products/architecture/a-profile/docs/arm-architecture-reference-manual-supplement-armv8-a.

———, ed. 2017b. "ARM c Language Extensions for Sve." 2017. https://developer.arm.com/docs/100987/latest/arm-c-language-extensions-for-sve.

Page 16 of 16 1.0

<sup>&</sup>lt;sup>2</sup>http://www.arm.com/about/trademarks